Semiconductor Products Sector Application Note **AN2183**

# Using FLASH as EEPROM on the MC68HC908GP32

By Derrick H.J. Klotz Field Applications Engineer Toronto, Canada

#### Introduction

This application note describes a method for using the on-chip FLASH memory of the MC68HC908GP32 as one would typically use EEPROM (electrically erasable programmable read-only memory). For the purposes of this application note, the FLASH memory that is manipulated via this method is referred to as "FlashEE." It is expected that the reader is somewhat familiar with the MC68HC908GP32/08GP32 Technical Data book, Motorola document order number MC68HC908GP32/H, as well as typical EEPROM device usage.

In many projects, EEPROMs are used as nonvolatile storage for calibration data, control information, data logging, etc. The FLASH memory technology employed in the M68HC908 Family of microcontrollers (MCU) is capable of being reprogrammed easily while the application software is executing. Project cost savings can be realized by simply using an appropriate section of the on-chip FLASH memory as one would use an off-chip EEPROM device.

In order to verify the correct operation of the FlashEE routines, a test program is included in this application note. This program demonstrates how these routines would be integrated into a project. The test program communicates with a host computer via a simple RS-232 connection in order to facilitate testing. User programs that include the FlashEE routines are free to implement them as one would commonly expect to use EEPROM algorithms for various forms of data storage.

# FlashEE Implementation

Specifications for the M68HC908 Family FLASH memory indicate a program/erase cycle endurance of 10,000 cycles across the full operating temperature range. This is typically more than sufficient for most applications. However, this value can be mathematically elongated by the number of times a small data block can fit within a FLASH erase page.

It is important to note that the while the FLASH memory is "page" erasable, it is, in fact, byte programmable. It's organization is configured for efficient "row" programming, but any algorithm must write each location on a byte-by-byte basis. There is no limit to the minimum number of bytes that must be programmed within a row. But every time a row is programmed, the high voltage charge pump must be enabled and disabled, regardless of the number of bytes that are programmed.

A critical FLASH memory specification is the cumulative program high voltage period. This is the maximum total time that a specific FLASH program row is subjected to being programmed between erasures. The technical data for the MC68HC908GP32 lists this maximum specification as being 4 ms.

The subroutines herein are optimized to program relatively small blocks of data sequentially within the FLASH memory, thereby minimizing the total cumulative length of time spent programming. These subroutines will only erase the FlashEE space when there is no more room for the next data block. Each FLASH erase page consists of two program rows. The FLASH erase page size for the MC68HC908GP32 is 128 bytes.

AN2183

If an example application uses a FlashEE data block size of four bytes, then 32 program cycles of four bytes each will be performed prior to executing a single erase cycle, at which point this would be considered one complete program/erase cycle. Hence, in this example, the FlashEE endurance would be calculated as being 320,000 program/erase cycles (in other words, 10,000 x 32).

The high voltage program time used by the subroutines herein to program four bytes is less than 150  $\mu$ s. Each program row would be subjected to a program cycle 16 times (remember, two program rows per erase page). This provides a cumulative time of less than 2.4 ms (150  $\mu$ s x 16), which is less than the maximum specification given.

The FLASH block protect register (FLBPR) points to the first FLASH memory location to be protected. When programmed, every location from that address to \$FFFF will be protected from accidental erasure. For this reason, it is easiest to assign the FlashEE sections to the very beginning of the FLASH memory, assuming that the FLBPR may be used to protect application code.

To simplify the FlashEE implementation, some essential guidelines have been used, specifically:

- FlashEE data is written in blocks of multiple bytes.

- Each FlashEE data block fits within a single FLASH program row.

- The first FlashEE data block byte to be written cannot be equal to \$FF.

Programming only one byte is possible, but may result in application code inefficiencies since an entire 128-byte FLASH erase page would need to be reserved for each single byte of FlashEE.

If the data storage space requirement exceeds the size of a single FLASH program row (i.e., more than 64 bytes on the MC68HC908GP32), then the data will need to be split up over multiple FlashEE sections, each occupying one FLASH erase page (i.e., 128 bytes on the MC68HC908GP32). If multiple FlashEE sections are used, they must be manipulated separately. This is demonstrated with the test program provided.

AN2183

As part of a search algorithm, the software interrogates the first byte location of each FlashEE data block to see if it is erased (i.e., \$FF). For this reason, when writing a new block of data, the first byte must not be \$FF. All subsequent data block locations have no restrictions on their stored value.

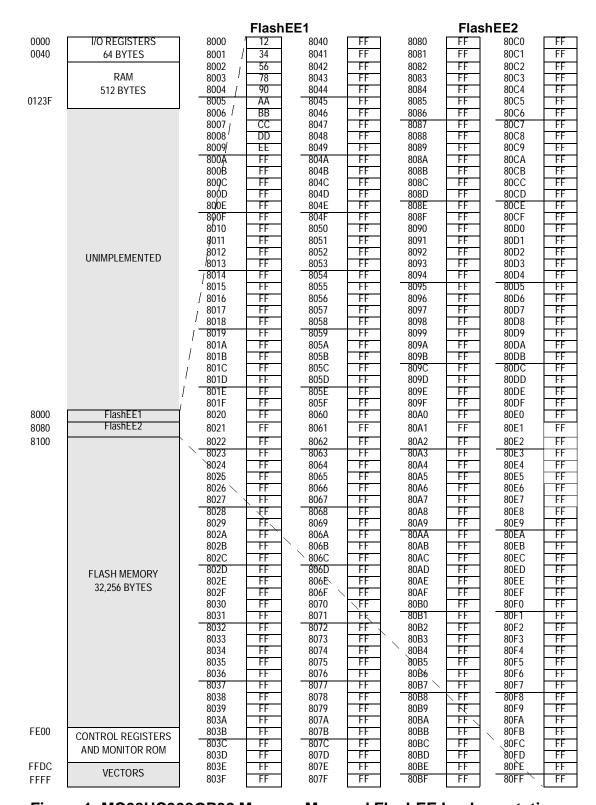

Figure 1 shows the MC68HC908GP32 memory map and the space occupied by two separate FlashEE sections (128 bytes each). Note that the erased state of the FLASH memory is \$FF and that the first 10 locations (\$8000 to \$8009) are not erased. This represents the current state of FlashEE1 at the end of the example host test session shown in Figure 2 and described later in this text.

As defined in the example provided, FlashEE1 starts at address \$8000 with a data block size of five bytes. FlashEE2 starts at address \$8080 and has a data block size of seven bytes. Although reasonably obvious, delineations are shown in **Figure 1** that demonstrate that neither five nor seven evenly fit into a FLASH program row that is 64 bytes in size. The routines provided will store the appropriate data sequentially in the respective FlashEE sections only up to the last complete available data block space. As defined, FlashEE1 will never store a value in the last four locations of its FLASH program row (i.e., locations \$803C to \$803F and \$807C to \$807F will always be erased.) Similarly, the last byte in each FLASH program row of FlashEE2 will also remain erased (i.e., locations \$80BF and \$80FF). A FlashEE section with a data block size of 33 to 64 bytes inclusive will only fit the data into each FLASH program row once, leaving the remaining locations erased.

The program files provided are:

- flashee.equ FlashEE subroutine operational parameter definitions

- **flashee.asm** FlashEE subroutines

- eetest.asm FlashEE test program

- gp32.equ MC68HC908GP32 microcontroller definitions

AN2183

Figure 1. MC68HC908GP32 Memory Map and FlashEE Implementation

# flashee.equ Subroutines

The FlashEE subroutines are tailored to the needs and operation conditions of a specific application by modifying the parameters provided in this file, which must be included near the top of the application program file. To help avoid assembly language label naming conflicts, all labels used in this file start with either "EE" or "Ram".

The parameters defined are grouped into three specific categories:

- Microcontroller FLASH memory parameters

- FlashEE data parameters

- Microcontroller bus frequency parameters

# Microcontroller FLASH Memory Parameters

The specific sizes of the FLASH memory program row and erase page are defined here (64 bytes and 128 bytes, respectively, for the MC68HC908GP32). Also, the erased state of a FLASH byte is also declared as \$FF.

These parameters are initially defined as:

| EE_FlashPage:              | equ | 128  |

|----------------------------|-----|------|

| EE_FlashRow:               | equ | 64   |

| <pre>EE_FlashErased:</pre> | equ | \$FF |

# FlashEE Data Parameters

The starting address of each FlashEE section is declared here. These parameters are not directly used by the FlashEE subroutines. They are passed forward by the application program when these subroutines are called. For demonstration purposes, two separate FlashEE sections are shown, although many more are possible.

The size of each FlashEE data block is also defined. Note that each FlashEE section can have its own unique data block size.

AN2183

#### The parameters for FlashEE1 are initially defined as:

#### The parameters for FlashEE2 are initially defined as:

| <pre>EE_StartAddr2:</pre> | equ | {EE_StartAddr2+EE_FlashPage} |

|---------------------------|-----|------------------------------|

| EE_BlockSize2:            | equ | 7                            |

Note that the assembler will assign the label "EE\_StartAddr2" with a value of \$8080.

# Microcontroller Bus Frequency Parameters

The FlashEE subroutines employ delay loops that must be tuned to the microcontroller bus frequency. The values for these parameters for a bus frequency of 7.3728 MHz are provided in the software listing. If a different bus frequency is desired, then these parameters must be changed in accordance with the formula provided, specifically:

Value = ((delay in

$$\mu$$

s) x (bus frequency in MHz) – 2) ÷ 3

As an example, a delay of 30  $\mu$ s with a bus frequency of 7.3728 MHz would result in the following:

RamDelay30 =

$$((30) \times (7.3728) - 2) \div 3 = 73.06 \cong 74$$

For a 7.3728-MHz bus frequency, the required parameters are initially defined as:

| RamDelay5:  | equ | 12  |

|-------------|-----|-----|

| RamDelay10: | equ | 24  |

| RamDelay30: | equ | 74  |

| RamDelay50: | equ | 122 |

### flashee.asm Subroutines

This file contains the FlashEE subroutine source code and must be included in the application program file. These subroutines only use local variables on the stack and, hence, do not require any other predefined global variable space resources. The maximum available stack space

AN2183

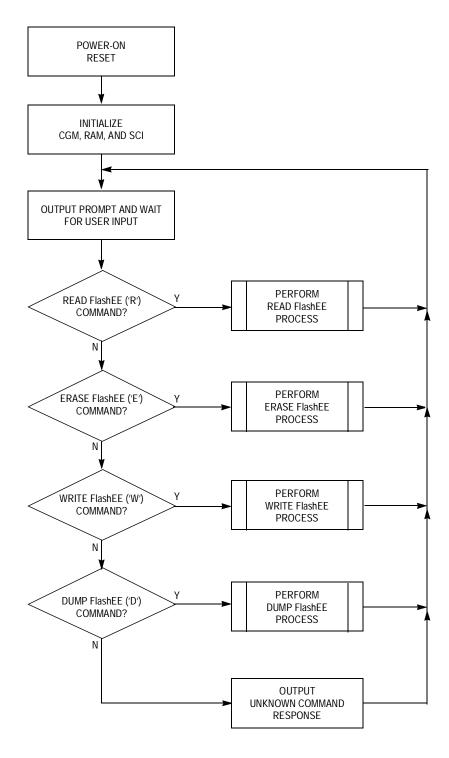

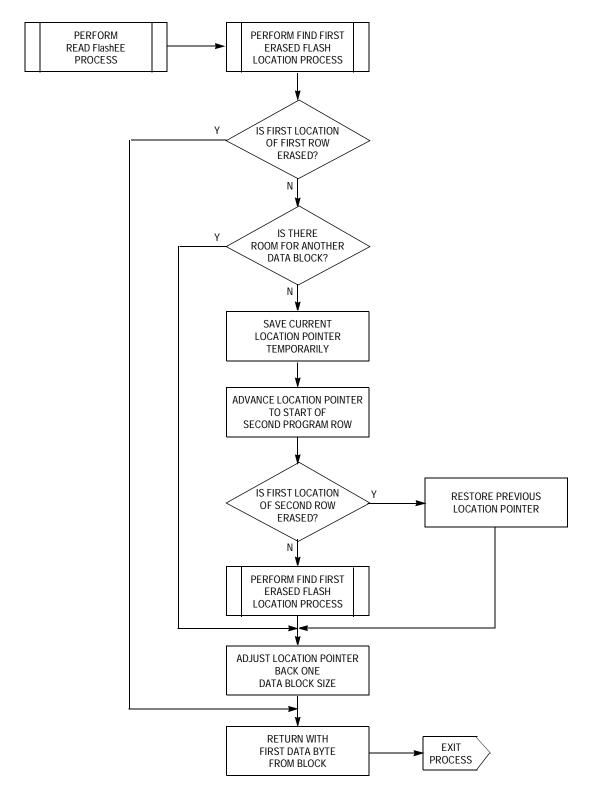

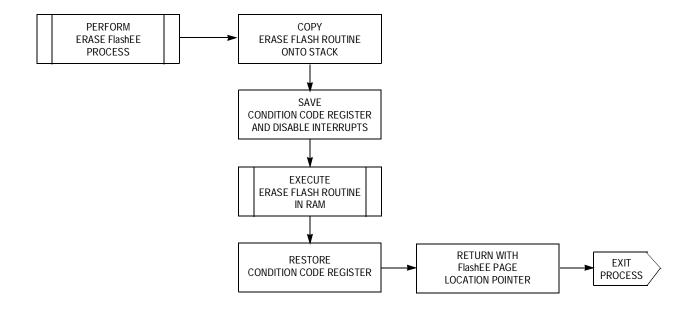

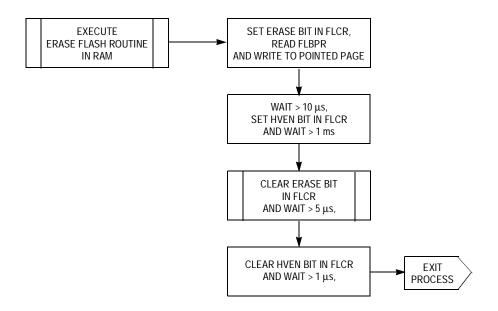

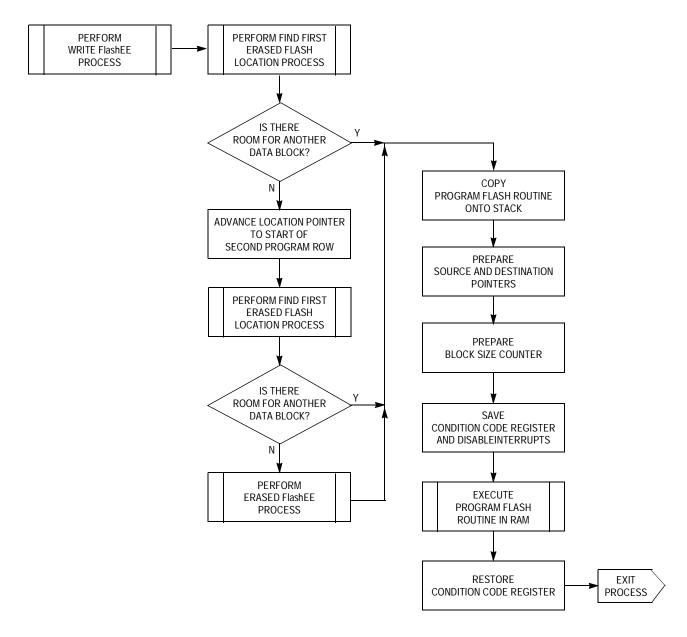

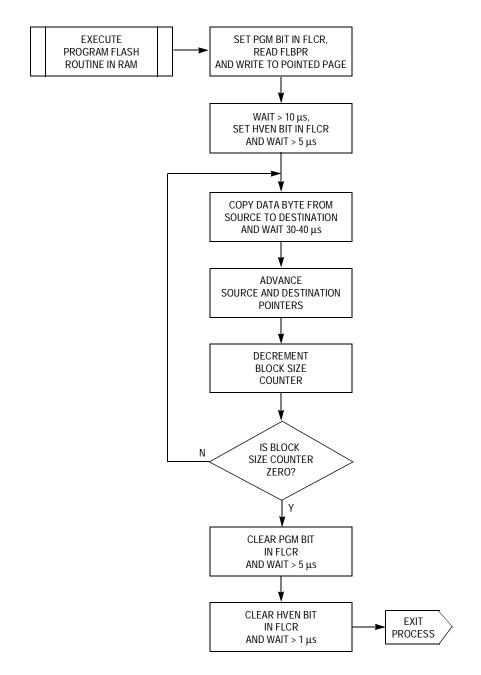

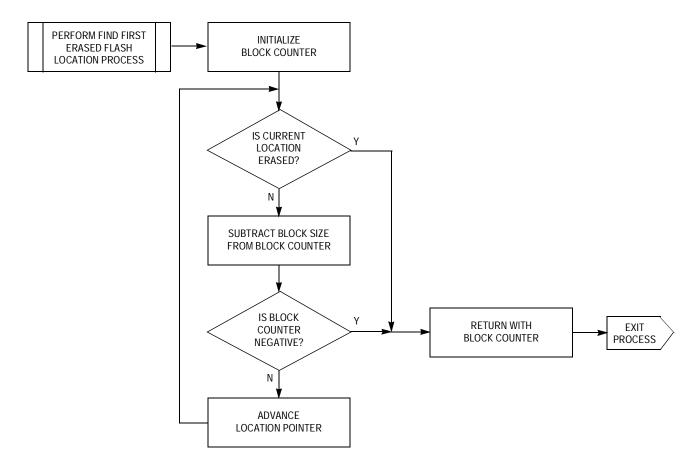

requirement is 80 bytes. To help avoid assembly language label naming conflicts, all labels used start with either "EE" or "Ram". The flow diagrams of these routines (with the exception of the Dump utility, due to its simplicity) are provided in **Figure 3** through **Figure 8**.

The available FlashEE routines are:

- EERead Read the current valid FlashEE data block

- EEErase Erase an entire FlashEE section

- EEWrite Write a new FlashEE data block

#### **EERead**

This subroutine is called with the 16-bit index register H:X pointing at the starting address of the desired FlashEE section and the accumulator preloaded with that FlashEE section's data block size. The FlashEE section is sequentially scanned, block by block, until an erased FLASH byte (i.e., \$FF) is found occupying the first location of a data block or the end of the section is reached.

This subroutine returns with the 16-bit index register H:X pointing to the first location of the most recent FlashEE data block and the data in that location stored in the accumulator. The calling routine should check the accumulator value for \$FF to see if any data has been stored in the FlashEE. Refer to Check\_Read subroutine in the eetest.asm. This check should only be needed when an EERead is performed before the very first EEWrite.

#### **EEErase**

This subroutine is used to erase the contents of a FlashEE section. It is called with the 16-bit index register H:X pointing at the starting address of the desired FlashEE section. The value in H:X is returned unchanged. Regardless of bus frequency, this subroutine will execute in just over one millisecond. (Specifically, at a bus frequency of 7.3728 MHz, this subroutine executes in about 1096 µs.)

Note that this subroutine will copy and execute a program in RAM. This is required due to the fact that erasing FLASH locations cannot be performed by code being executed from the FLASH memory. While executing code from RAM, all interrupts are disabled.

AN2183

#### **EEWrite**

This subroutine requires two address pointers when called. The 16-bit starting address of the desired FlashEE section must be saved on the stack just prior to calling this subroutine. In addition, the 16-bit index register H:X must point to the first byte of a source data block, which is typically a buffer located in RAM. As well, the accumulator is preloaded with the FlashEE data block size. This subroutine will then copy the required number of bytes sequentially from the source location into the FlashEE.

As a point of reference toward understanding the speed of this subroutine, consider using a data block of 16 bytes and a bus frequency of 7.3728 MHz. The best case programming time would be about 644  $\mu s$ . The worst case would involve writing the data block into the FlashEE with no available room. This requires that the FlashEE first be erased prior to programming the data. In this given scenario, this subroutine executes in about 1772  $\mu s$ , of which just over 1000  $\mu s$  is due to the FlashEE erasure procedure.

Note that this subroutine will copy and execute a program in RAM. This is required due to the fact that programming FLASH locations cannot be performed by code being executed from the FLASH memory. While executing code from RAM, all interrupts are disabled.

#### eetest.asm Subroutines

This file provides an executable demo program used to test and verify the use of the FlashEE subroutines and files. Note that the files **flashee.equ**, **flashee.asm**, and **gp32.equ** are incorporated in this test program via the "include" assembler directive.

A simple user interface is provided via the on-chip serial communications interface (SCI) and industry standard RS232 communications with a host computer executing a simple terminal program. The serial bit rate is configured for 115.2 kbaud.

The software implements four single ASCII character commands (case insensitive) and provides the ability to test and interrogate two separate

AN2183

FlashEE sections. Each command is followed by either "1" or "2" to indicate the desired FlashEE section.

The commands are:

- R Read FlashEE

- E Erase FlashEE

- W Write FlashEE

- D Dump FlashEE

An example of the host terminal display during a simple test session using FlashEE1 with a block size of five bytes is shown in **Figure 2**. The program implements a default prompt to the user of FlashEE>.

The first user command is d1, or "dump the contents of FlashEE1." All 128 bytes are printed out in a format that is relatively easy to read. Note that at this point, the entire FlashEE section is erased (i.e., all locations contain \$FF). The second command issued is r1, or "read the most recent FlashEE1 data block." Since FlashEE1 is erased, a message is sent indicating that no data is currently stored in FlashEE1.

Next, the user has requested that a block of data be written into FlashEE1 with w1. The program responds with an equal sign (=) and then accepts the correct number of hexadecimal values (five in total for FlashEE1). The user verifies that the data has been programmed correctly by first using the x1 command, and secondly with d1 which clearly indicates where the data has been stored.

The user enters another block of data with the next w1 command. The following d1 entry shows that the new data has been correctly stored in the next data block location. And the next x1 command confirms that the read subroutine correctly identifies which is the most recent data.

Continuing with this method, the demo program provided was used to test and verify the correct operation of the FlashEE subroutines.

```

FlashEE>d1

FF FF

FlashEE>r1 FlashEE erased

FlashEE>w1=12 34 56 78 90

FlashEE>r1 12 34 56 78 90

FlashEE>d1

12 34 56 78 90 FF FF

FF FF FF FF FF FF FF FF FF FF FF FF FF

FF FF FF FF FF FF FF FF FF FF FF

FlashEE>w1= aa bb cc dd ee

FlashEE>d1

12 34 56 78 90 AA BB CC DD EE FF FF FF FF FF

FF FF FF FF FF FF FF FF FF FF FF

FF

FF

FlashEE>r1 AA BB CC DD EE

FlashEE>

```

Figure 2. Simple Host Terminal Test Session Display

#### Read FlashEE (R)

After entering the single character R, followed by either "1" or "2", the program will respond by outputting the most recent data byte block. In the example shown, the first time R is entered and the FlashEE is erased as indicated by the software's response. Subsequent examples show the current data block data being reported back to the host.

#### **Erase FlashEE (E)**

AN2183

This command will directly execute the EEErase subroutine and erase the selected FlashEE section.

#### Write FlashEE (W)

After entering the single character W, followed by either "1" or "2", the program will respond by prompting the user to enter a data block string of data. Each entry must be a valid hexadecimal value and is echoed back as typed. Entering a non-hexadecimal value results in the process being stopped with the default prompt being output. After entering the required number of bytes, the FlashEE is programmed with the data provided.

#### **Dump FlashEE (D)**

This command will output the current contents of the selected FlashEE section.

# **Summary**

Most projects using the M68HC908 Family of microcontrollers requiring nonvolatile data storage that is application software programmable need not incur the added cost of external EEPROM devices. A method for using the on-chip FLASH memory for such application purposes has been demonstrated with this application note.

Figure 3. eetest.asm Software Flow Diagram

Figure 4. Read FlashEE Software Flow Diagram

Figure 5. Erase FlashEE Software Flow Diagrams

Figure 6. Write FlashEE Software Flow Diagram

Figure 7. Write FlashEE RAM Routine Software Flow Diagram

Figure 8. Find First Erased FlashEE Data Block Software Flow Diagram

# flashee.equ

```

Flash as EEPROM - MC68HC908GP32

; *

Copyright (c) Motorola, 2001

; *

This file provides the application specific parameters for the FlashEE routines.

This program has been specially tailored towards the MC68HC908GP32.

; *

; *

; *

Current Release Level:

File name:

flashee.equ

Last Edit Date:

15-Jun-01

Classification:

; *

Include Files:

gp32.equ

: MC68HC908GP32 MCU definitions

; *

; *

Assembler:

P&E's CASM08Z

Version: 3.16

; *

; *

Target:

MC68HC908GP32

; *

;*

Documentation:

MC68HC908GP32/H Rev 3

; *

Motorola Microcontroller Technical Data

; *

; *

; *

Author:

DHJ Klotz

; *

First Release:

15-Jun-01

; *

; *

Update History:

; *

;*

Date Author Description of Change

; *

_____

; *

ES 1.0 15-Jun-01 DHJK Initial release.

; *

; * *

; *

; *

Notes:

; *

- This file is intended to be included within another source program along with

; *

the program file "flashee.asm". All labels used in this file start with either

"EE" or "Ram".

; *

; *

; *

- The "FlashEE Data Parameters" and "Microcontroller Bus Frequency Parameters"

; *

declared at the start of this listing must be tailored to the specific needs of

; *

the target application prior to using the programs herein.

; *

; *

; *

Motorola reserves the right to make changes without further notice to any product

; *

herein to improve reliability, function, or design. Motorola does not assume any

; *

liability arising out of the application or use of any product, circuit, or software

; *

described herein; neither does it convey any license under its patent rights nor the

rights of others. Motorola products are not designed, intended, or authorized for

```

#### AN2183

```

; *

use as components in systems intended for surgical implant into the body, or other

; *

applications intended to support life, or for any other application in which the

; *

failure of the Motorola product could create a situation where personal injury or

;*

death may occur. Should Buyer purchase or use Motorola products for any such

;*

intended or unauthorized application, Buyer shall indemnify and hold Motorola and

;*

its officers, employees, subsidiaries, affiliates, and distributors harmless against

;*

all claims, costs, damages, and expenses, and reasonable attorney fees arising out

;*

of, directly or indirectly, any claim of personal injury or death associated with

; *

such unintended or unauthorized use, even if such claim alleges that Motorola was

;*

negligent regarding the design or manufacture of the part.

; *

; *

Motorola and the Motorola logo are registered trademarks of Motorola Ltd.

; *

; *

; *

;* These parameters reflect the specific FLASH memory characteristics of the MC68HC908GP32.

;* The FlashEE software can be easily ported to other MC68HC908 family members by changing

;*

the parameters listed here.

; *

EE_FlashPage:

equ

128

; Flash Erase Page size

64

EE_FlashRow:

equ

; Flash Program Row size

EE_FlashErased: equ

SFF

; Flash erased state

; *

;* By default, the very first Flasherase page is assigned for FlashEE usage, so that the

; *

rest of the Flash memory can be protected via the Flash Block Protect Register (FLBPR).

; *

EE_StartAddr1: equ

$8000

; starting address of 1st FlashEE

EE_StartAddr2: equ

{EE_StartAddr1+EE_FlashPage}

; starting address of 2nd FlashEE

; *

; *

; *

The data block size for each FlashEE section is defined here. Each must be less than or

equal to "EE_FlashRow"

; *

; *

EE_BlockSize1: equ

5

; data block size for 1st FlashEE

EE_BlockSize2: equ

; data block size for 2nd FlashEE

; *

; *

; *

Software delay loops are initially calculated for a 7.3728 MHz bus frequency. For other

; *

frequencies, the following parameters must be modified accordingly.

; *

Microsecond delay parameter calculation is ((N \times bus \ clock) - 2) / 3

;*

; *

For example,

; *

if bus = 7.3728 MHz, then 10us ->

((10us \times 7372800 - 2)) / 3 = 23.9 = 24

; *

; *

As a check, use ((M \times 3) +2) / bus clock

; *

For example,

; *

if bus = 7.3728 MHz, then for N = 24 -> ((24 \times 3) + 2) / 7372800 = 10us

; *

RamDelay5:

12

; 5us delay parameter

eau

RamDelay10:

eau

2.4

; 10us delay parameter

RamDelay30:

equ

74

; 30us delay parameter

RamDelay50:

equ

122

; 50us delay parameter

```

20 MOTOROLA

AN2183

#### flashee.asm

```

;* Flash as EEPROM - MC68HC908GP32

;*

Copyright (c) Motorola, 2001

; *

; *

This file provides the low level assembly routines for using the Flash as EEPROM.

;* This program has been specially tailored towards the MC68HC908GP32.

; *

;* File name:

flashee.asm

Current Release Level:

1.0

;* Last Edit Date:

15-Jun-01

Classification:

;*

;* Include Files:

gp32.equ : MC68HC908GP32 MCU definitions flashee.equ : FlashEE parameters

gp32.equ

;*

; *

;* Assembler:

P&E's CASM08Z

Version: 3.16

; *

;* Target:

MC68HC908GP32

; *

MC68HC908GP32/H Rev 3

;* Documentation:

;*

Motorola Microcontroller Technical Data

; *

; *

;* Author:

DHJ Klotz

;* First Release:

15-Jun-01

; *

;* Update History:

;*

;* Rev

Date Author Description of Change

; *

_____

; *

ES 1.0 15-Jun-01 DHJK Initial release.

; *

; *

;* Notes:

;*

- This file is intended to be included within another source program along with

; *

the FlashEE parameter file "flashee.equ". All labels used in this file start with

; *

either "EE" or "Ram".

; *

; *

- The "FlashEE Data Parameters" and "Microcontroller Bus Frequency Parameters"

declared in the include file "flashee.equ" must be tailored to the specific needs

; *

; *

of the target application prior to using the programs herein.

; *

; *

- Callable subroutines are:

;*

EERead : returns with H:X pointing to first FlashEE data block entry

;*

EEWrite: programs FlashEE with data block pointed to by H:X

; *

EEErase : erases entire FlashEE space pointed to by H:X

; *

```

AN2183

```

; *

; *

Motorola reserves the right to make changes without further notice to any product

; *

herein to improve reliability, function, or design. Motorola does not assume any

;*

liability arising out of the application or use of any product, circuit, or software

;*

described herein; neither does it convey any license under its patent rights nor the

;*

rights of others. Motorola products are not designed, intended, or authorized for

;*

use as components in systems intended for surgical implant into the body, or other

; *

applications intended to support life, or for any other application in which the

;*

failure of the Motorola product could create a situation where personal injury or

; *

death may occur. Should Buyer purchase or use Motorola products for any such

; *

intended or unauthorized application, Buyer shall indemnify and hold Motorola and

;*

its officers, employees, subsidiaries, affiliates, and distributors harmless against

; *

all claims, costs, damages, and expenses, and reasonable attorney fees arising out

; *

of, directly or indirectly, any claim of personal injury or death associated with

; *

such unintended or unauthorized use, even if such claim alleges that Motorola was

;*

negligent regarding the design or manufacture of the part.

; *

; *

Motorola and the Motorola logo are registered trademarks of Motorola Ltd.

; *

;*

; *

; *

This subroutine expects H:X to be pointing to the first FlashEE page location and returns

; *

with H:X pointing to the most recent FlashEE data. The FlashEE data block size is passed

;*

forward in ACC.

; *

; *

Calling convention:

; *

; *

ldhx

#EE_StartAddr

;*

#EE_BlockSize

lda

; *

jsr

EERead

; *

H:X -> FlashEE block address

; *

Returns:

; *

ACC = first FlashEE data byte

;*

; *

everything

Changes:

; *

EERead:

;

Find first erased location within FlashEE page.

;

Check for room within first FlashEE row.

If the entire row is erased, then return with H:X unchanged. If the next available

erased FlashEE block is within the first program row, then return pointing to the

block just before it.

; save FlashEE data block size

psha

; save FlashEE address lsb on stack

pshx

; go find next free location

bsr

EEFindFirst

; check if start of 1st row is 1st blank location

срх

1,sp

beq

EERead3

; exit if so

cmp

2,sp

; check if there's room for another data block

bpl

EERead2

; exit if so

Check for room within second FlashEE row.

```

22 MOTOROLA

AN2183

```

If the second row is erased, then return pointing to the last block in the first row.

Otherwise, return pointing to the last used block in the second row.

;

; save current address lsb

txa

; restore FlashEE address lsb

pulx

#EE_FlashRow

; H:X now points to second program row

aix

; save previous address lsb on stack

psha

lda

; check if first location

cmp

#EE_FlashErased

; is erased

EERead1

; skip if so

bne

; else, restore previous FlashEE address lsb

pulx

; put back on stack for clean exit

pshx

bra

EERead2

; and exit

EERead1:

lda

2,sp

; get FlashEE data block size

bsr

EEFindFirst

; go find next free location

EERead2:

txa

; perform

sub

2,sp

; 16-bit subtraction

tax

in order

to adjust

pshh

FlashEE pointer

pula

sbc

#0

backwards

psha

one data block

pulh

size

EERead3:

ais

#2

; deallocate stack usage

lda

; get first FlashEE data byte

, x

rts

; return

RAM Executable FlashEE Page Erase Subroutine ===================================

; *

; *

This subroutine will erase the Flash memory page that is being pointed to by H:X.

; *

This subroutine is copied into and executed from RAM and expects to be called via

; *

"jsr ,x".

;*

RamEraseEE:

Retrieve page address.

psha

; save previous CCR on stack

lda

{RamEraseSize},x

; get msb

{RamEraseSize+1},x

ldx

; and lsb of address

psha

; put msb

; into HREG

pulh

;

Step 1:

;

Set ERASE, read the Flash Block Protect Register and write any data into Flash page.

;

;

lda

#{ERASE}

; set ERASE control bit

flcr

; in Flash Control Register

sta

flbpr

; read from Flash Block Protect Register

lda

; write any data to address within page

sta

, x

;

```

```

Step 2:

Wait for >10us, then set HVEN.

;

lda

#RamDelay10

; wait

dbnza

; for 10us

lda

#{ERASE | HVEN}

; set HVEN control bit

sta

flcr

; in Flash Control Register

Step 3:

;

Wait for >1ms, then clear ERASE.

;

#20

ldx

; outer loop

RamEraseEE1:

; set for 20x

lda

#RamDelay50

; inner loop

dbnza

; set for 50us

dbnzx

{\tt RamEraseEE1}

; loop back until done

#{HVEN}

lda

; clear ERASE control bits

sta

flcr

; in Flash Control Register

;

Step 4:

;

Wait for >5us, then clear HVEN, then wait >1us and return.

;

lda

#RamDelay5

; wait

dbnza

; for 5us

clra

; clear HVEN control bit

sta

flcr

; in Flash Control Register

pula

; retreive previous CCR

; wait for at least lus before

brn

returning

rts

{*-RamEraseEE}

RamEraseSize:

equ

;*

;*

;*

This subroutine will erase the Flash memory page that is being pointed to by H:X.

; *

60 bytes of stack space is used, including this subroutine's call return address.

; *

; *

Calling convention:

; *

; *

ldhx

#EE_StartAddr

jsr

; *

EEErase

; *

; *

Returns:

H:X unchanged

;*

;*

Changes:

ACC

; *

EEErase:

pshx

; save pointer

pshh

; on stack

;

Copy FlashEE page erase routine into RAM

;

ldhx

#RamEraseSize

; initialize pointer

```

```

EEErase1:

; get program from Flash

lda

RamEraseEE-1,x

psha

; copy into Stack

dbnzx

EEErase1

; decrement pointer and loop back until done

;

;

Execute program routine in RAM.

tsx

; use H:X to point to RAM executable routine

tpa

; get CCR

sei

; disable all interrupts

jsr

; erase Flash page

ais

#RamEraseSize

; deallocate stack space used

; restore

pulh

pulx

address pointer

tap

; restore previous CCR

rts

; return

; *

; *

; *

This subroutine is used to find the first erased FlashEE block, starting at the

;*

address being pointed to by H:X. The FlashEE data block size is passed forward in ACC.

;*

; *

Calling convention:

;*

;*

ldhx

#address

;*

lda

#EE_BlockSize

;*

jsr

EEFindFirst

;*

H:X -> first erased FlashEE block address

Returns:

; *

ACC = number of erased FlashEE bytes left

; *

CCRZ = set if erased location successfully found, otherwise clear

; *

; *

Changes:

everything

; *

EEFindFirst:

; save FlashEE data block size

psha

lda

#EE_FlashRow

; get Flash Program Row size

psha

; save on stack as a counter

EEFindFirst1:

lda

#EE FlashErased

; get erased Flash data

cmp

, x

; check if Flash location is erased

beq

EEFindFirst2

; exit if so

pula

; else, get counter

sub

1,sp

; adjust by subtracting block size

EEFindFirst3

; exit if out of room

bmi

; else, save new count

psha

txa

; perform

add

2,sp

; 16-bit addition

in order

tax

to advance

pshh

pula

FlashEE pointer

adc

#0

forwards

psha

to the

next block

pulh

bra

EEFindFirst1

; loop back

```

```

EEFindFirst2:

; retrieve remaining erased bytes count

pula

EEFindFirst3:

ais

; deallocate stack usage

rts

;*

;*

This subroutine will write the block of data being pointed to by H:X into the FlashEE.

;* 80 bytes of stack space is used, including this subroutine call return address. The

;* FlashEE data block size is passed forward in ACC.

; *

; *

Calling convention:

; *

; *

ldhx

#EE_StartAddr

;*

pshx

; *

pshh

; *

ldhx

#BlockSourceAddress

; *

#EE_BlockSize

lda

; *

jsr

WriteEE

; *

ais

#2

; *

; *

nothing

Returns:

;*

;*

Changes:

everything

; *

EEWrite:

; save FlashEE data block size

psha

pshx

; save block

; source pointer

pshh

;

Check for room within first FlashEE row.

;

; get first FlashEE row address lsb

ldx

7,sp

lda

; get first FlashEE

6,sp

psha

; row address

pulh

msb

lda

; get FlashEE data block size

3,sp

EEFindFirst

bsr

; go find next free location

3,sp

; check if there's room for another data block

cmp

bpl

EEWrite1

; continue if so

;

Check for room within second FlashEE row (which is within the same erase page).

ldx

7,sp

; get first FlashEE row address lsb

lda

6,sp

; get first FlashEE

psha

; row address

pulh

msb

aix

#EE_FlashRow

; H:X now points to second program row

lda

; get FlashEE data block size

3,sp

EEFindFirst

; go find next free location

bsr

; check if there's room for another data block

cmp

3,sp

EEWrite1

; continue if so

bpl

```

```

If there's no room, then erase entire FlashEE page.

ldx

7,sp

; get first FlashEE row address lsb

lda

6,sp

; get first FlashEE

psha

; row address

pulh

bsr

EEErase

; erase entire FlashEE page

EEWrite1:

; save block

pshx

pshh

; destination pointer

;

Copy FlashEE byte program routine into RAM

ldhx

#RamWriteSize

; initialize program size counter

EEWrite2:

lda

RamWriteEE-1,x

; get program from Flash

psha

; copy onto stack

dbnzx

EEWrite2

; decrement pointer and loop back until done

;

Prepare source and destination pointers and FlashEE block byte counter.

;

tsx

; use H:X to point to RAM executable routine

lda

{RamWriteSize+2},x

; get source address msb

{RamWriteSRC},x

; save it in RAM executable routine

sta

lda

{RamWriteSize+3},x

; get source address lsb

{RamWriteSRC+1},x

sta

; save it in RAM executable routine

{RamWriteSize},x

lda

; get destination address msb

{RamWriteDST1},x

; save it in

sta

{RamWriteDST2},x

; RAM executable routine

sta

lda

{RamWriteSize+1},x

; get destination address lsb

{RamWriteDST1+1},x

sta

; save it in

sta

{RamWriteDST2+1},x

; RAM executable routine

;

Execute program routine in RAM.

;

; get CCR for current I-bit status

tpa

; disable all interrupts

sei

; write data into Flash

jsr

, X

;

ais

#{RamWriteSize+5}

; deallocate stack space used

tap

; restore previous CCR, specifically the I-bit

rts

; return

;* RAM Executable FlashEE Block Program Subroutine ==============================

; *

; *

This subroutine controls the FlashEE block programming sequence.

;*

This subroutine is copied into and executed from RAM. It is self-modifying and expects

;*

to be called via "jsr ,x".

```

```

RamWriteEE:

; save previous CCR on stack

psha

;

Step 1:

;

Set PGM, read the Flash Block Protect Register and write any data to first Flash address.

;

lda

#{PGM}

; set PGM control bit

sta

flcr

; in Flash Control Register

lda

flbpr

; read from Flash Block Protect Register

"RamWriteDST1" is location offset relative to "RamWriteEE".

;

This RAM location is used as a 16-bit destination address pointer.

RamWriteDST1:

{*-RamWriteEE+1}

eau

sta

$FFFF

; write any data to first Flash address

;

Step 2:

;

;

Wait for >10us, then set HVEN, then wait for >5us.

;

lda

#RamDelay10

; wait

dbnza

; for 10us

#{PGM | HVEN}

; set HVEN control bit

lda

; in Flash Control Register

sta

flcr

lda

#RamDelay5

; wait

dbnza

; for 5us

Step 3:

;

Write data to Flash and wait for 30 - 40us. Repeat until done.

;

RamWriteEE1:

;

"RamWriteSRC" is location offset relative to "RamWriteEE".

;

This RAM location is used as a 16-bit source address pointer.

;

;

RamWriteSRC:

{*-RamWriteEE+1}

eau

lda

$777

; get data

;

"RamWriteDST2" is location offset relative to "RamWriteEE".

;

This RAM location is used as a 16-bit destination address pointer.

;

;

RamWriteDST2:

{*-RamWriteEE+1}

eau

SFFFF

; write data to Flash

sta

;

;

Advance source and destination pointers.

This sequence requires between 14 to 22 cycles.

;

inc

{RamWriteDST2+1},x

; advance the destination address lsb

bne

RamWriteEE2

; skip if no overflow

; else, advance the destination address msb

RamWriteDST2,x

inc

RamWriteEE2:

{RamWriteSRC+1},x

inc

; advance the source address 1sb

RamWriteEE3

bne

; skip if no overflow

inc

RamWriteSRC,x

; else, advance the source address msb

```

```

RamWriteEE3:

#{RamDelay30-4}

; wait

dbnza

; for a total of 30us

dbnz

{RamWriteSize+8},sp,RamWriteEE1 ; decrement byte counter, loop back til done

;

;

Step 4:

Clear PGM and wait for >5us.

#{HVEN}

; clear PGM control bit

lda

sta

flcr

; in Flash Control Register

lda

#RamDelay5

; wait

dbnza

; for 5us

Step 5:

;

Clear HVEN, wait >1us and return.

;

; clear HVEN control bit

clra

sta

flcr

; in Flash Control Register

; retreive previous CCR

pula

; wait for at least 1us before

brn

rts

returning

{*-RamWriteEE}

RamWriteSize:

equ

```

#### eetest.asm

```

.header 'MC68HC908GP32 Flash as EEPROM Test'

.pagewidth 130

.pagelength 90

;* Flash as EEPROM Test - MC68HC908GP32

; *

Copyright (c) Motorola, 2001

; *

Test program for FlashEE.

; *

; *

;* File name:

eetest.asm

Current Release Level:

;* Last Edit Date:

15-Jun-01

Classification:

; *

: MC68HC908GP32 MCU definitions

;* Include Files:

gp32.equ

; *

flashee.equ

: FlashEE parameters

: FlashEE routines

;*

flashee.asm

; *

; *

P&E's CASM08Z

Assembler:

Version: 3.16

; *

;* Target:

MC68HC908GP32

; *

MC68HC908GP32/H Rev 3

;* Documentation:

; *

Motorola Microcontroller Technical Data

; *

; *

; * Author:

DHJ Klotz

;* First Release:

15-Jun-01

; *

;* Update History:

; *

Date Author Description of Change

;* Rev

; *

_____

; *

ES 1.0 15-Jun-01 DHJK Initial release.

; *

; * *

;*

; *

Notes:

; *

; *

; *

Motorola reserves the right to make changes without further notice to any product

; *

herein to improve reliability, function, or design. Motorola does not assume any

;*

liability arising out of the application or use of any product, circuit, or software

; *

described herein; neither does it convey any license under its patent rights nor the

; *

rights of others. Motorola products are not designed, intended, or authorized for

;*

use as components in systems intended for surgical implant into the body, or other

; *

applications intended to support life, or for any other application in which the

failure of the Motorola product could create a situation where personal injury or

```

```

; *

death may occur. Should Buyer purchase or use Motorola products for any such

; *

intended or unauthorized application, Buyer shall indemnify and hold Motorola and

; *

its officers, employees, subsidiaries, affiliates, and distributors harmless against

; *

all claims, costs, damages, and expenses, and reasonable attorney fees arising out

; *

of, directly or indirectly, any claim of personal injury or death associated with

;*

such unintended or unauthorized use, even if such claim alleges that Motorola was

; *

negligent regarding the design or manufacture of the part.

;*

;*

Motorola and the Motorola logo are registered trademarks of Motorola Ltd.

simulate

; enable simulation situational assembly

.set

; *

nolist

include "gp32.equ"

; include microcontroller definitions file

list

init_config2: equ

%00000001

; initial Configuration Register 2

%00000001

init_config1: equ

; initial Configuration Register 1

init_stack:

ram_last

; initialize stack pointer to last RAM location

equ

;***** Serial Communications Interface (SCI)

; *

%01000000

; initial SCI Control Register 1

init_scc1:

equ

%00001100

; initial SCI Control Register 2

init_scc2:

equ

init_scc3:

%0000000

; initial SCI Control Register 3

equ

%00000000

init_scbr:

equ

; initial SCI Baud Rate Register

include "flashee.equ"

; include FlashEE paramters file

ram_start

org

buffer:

64

dя

; generic input data buffer

; *

; *

ora

$9000

Start:

copctl

; clear the COP counter

sta

mov

#init_config2,config2

; initialize Configuration Register 2

mov

#init_config1,config1

; initialize Configuration Register 1

ldhx

#init_stack+1

; initialize

txs

; the stack pointer

Initialize the CGM for 7.3728 MHz bus speed from 32.768 kHz crystal.

ldhx

#bus7372800

; point to 7.372800 MHz parameters

jsr

PLLset

; change bus speed

```

```

Clear all RAM.

ldhx

#ram_start

; point to start of RAM

ClearRAM:

clr

, x

; clear RAM location

aix

#1

; advance pointer

cphx

#ram_last+1

; done ?

bne

ClearRAM

; loop back if not

Initialize Port I/O and Variables

;

#init_scc1,scc1

; initialize SCI Control Register 1

mov

#init_scc2,scc2

; initialize SCI Control Register 2

mov

mov

#init_scc3,scc3

; initialize SCI Control Register 3

#init_scbr,scbr

mov

; initialize SCI Baud Rate Register

;

cli

; enable all interrupts

;*

; *

;*

Interface commands:

; *

; *

'W' = write following sting into FlashEE

; *

'R' = read back current FlashEE block data

; *

'D' = dump entire FlashEE

;*

'E' = erase entire FlashEE

; *

'R′

cmd_read:

; Read command

equ

cmd_erase:

'E'

; Erase command

equ

'W′

cmd_write:

equ

; Write command

'D'

cmd_dump:

; Dump command

equ

;

main:

#msg_hello

ldhx

; point to hello message

PrintString

jsr

; output it

; get a character from the SCI

GetChar

jsr

#ascii_CR

; check for ASCII carriage return

cmp

beq

; just loop back if so

main

jsr

; else, echo character back

PutChar

#$DF

; convert to uppercase

and

;

;

;

Check_Read:

; check for Read command

#cmd read

cmp

bne

Check_Erase

; skip if not

;

jsr

GetChar

; get a character from the SCI

jsr

PutChar

; echo character back

#'1'

; check if target is 1st FlashEE

cmp

; continue if so

beq

Check_Read1

#'2'

; check if target is 2nd FlashEE

cmp

beq

Check_Read2

; continue if so

Check_What

; else, respond to unknown command

qmţ

```

```

Check_Read1:

; point to start of 1st FlashEE

ldhx

#EE_StartAddr1

lda

#EE_BlockSize1

; get 1st FlashEE data block size

bra

Check_Read3

; continue

Check_Read2:

ldhx

#EE_StartAddr2

; point to start of 2nd FlashEE

lda

#EE_BlockSize2

; get 2nd FlashEE data block size

Check_Read3:

; save FlashEE data block size on stack

psha

jsr

EERead

; move pointer to FlashEE data

cmp

#EE_FlashErased

; check if data is erased

bne

Check_Read4

; skip if not

pula

; else, deallocate stack usage

ldhx

#msg_erased

; point to FlashEE erased message

jsr

PrintString

; output it

bra

main

; loop back to top

Check_Read4:

# ′ ′

lda

; output

PutChar

jsr

; a space

lda

, X

; read FlashEE data

; output it

jsr

PutHexByte

aix

#1

; advance FlashEE pointer

1,sp,Check_Read4

dbnz

; loop back until done

; deallocate stack usage

pula

bra

main

; loop back to top

;

Check_Erase:

#cmd_erase

; check for Erase command

cmp

Check_Write

; skip if not

bne

;

GetChar

; get a character from the SCI

jsr

; echo character back

jsr

PutChar

#'1'

; check if target is 1st FlashEE

cmp

; continue if so

beq

Check_Erase1

#'2'

; check if target is 2nd FlashEE

cmp

beq

Check_Erase2

; continue if so

Check_What

; else, respond to unknown command

jmp

Check_Erase1:

ldhx

#EE_StartAddr1

; point to start of 1st FlashEE

bra

Check_Erase3

; continue

Check_Erase2:

ldhx

#EE_StartAddr2

; point to start of 2nd FlashEE

Check_Erase3:

jsr

EEErase

; Erase FlashEE

ldhx

#msg_erased

; point to FlashEE erased message

jsr

PrintString

; output it

bra

main

; loop back to top

;

```

```

Check_Write:

; check for Write command

#cmd_write

cmp

Check_Dump

; skip if not

bne

jsr

GetChar

; get a character from the SCI

jsr

PutChar

; echo character back

#111

; check if target is 1st FlashEE

cmp

Check_Write1

; continue if so

beq

#'2'

; check if target is 2nd FlashEE

cmp

Check_Write2

; continue if so

beq

jmp

Check_What

; else, respond to unknown command

Check_Write1:

ldhx

#EE_StartAddr1

; point to start of 1st FlashEE

lda

#EE_BlockSize1

; get 1st FlashEE data block size

bra

Check_Write3

; continue

Check_Write2:

; point to start of 2nd FlashEE

ldhx

#EE_StartAddr2

lda

#EE_BlockSize2

; get 2nd FlashEE data block size

Check_Write3:

; save FlashEE address lsb temporarily

pshx

; save FlashEE address msb temporarily

pshh

; save FlashEE data block size temporarily

psha

; initialize a counter with value too

psha

# ' = '

lda

; output '=' to indicate

jsr

PutChar

; ready for data

ldhx

#buffer

; reset buffer pointer

Check_Write4:

GetHexByte

; go retrieve data byte

jsr

bne

Check_What

; output error if not hexadecimal

sta

, x

; save data in buffer

# ' '

lda

; output

jsr

PutChar

; a space

; advance buffer pointer

aix

#1

; loop back until entire FlashEE block received

dbnz

1,sp,Check_Write4

pula

; deallocate stack usage

;

; retrieve FlashEE data block size

pula

ldhx

#buffer

; point to buffer (FlashEE address is on stack)

jsr

EEWrite

; write data into FlashEE

#2

; deallocte stack usage

ais

; loop back to top

qmţ

main

Check for Dump command and execute.

Check_Dump:

#cmd_dump

; check for Dump command

cmp

bne

Check_What

; skip if not

;

GetChar

; get a character from the SCI

jsr

jsr

PutChar

; echo character back

; check if target is 1st FlashEE

#'1'

cmp

; continue if so

beq

Check_Dump1

; check if target is 2nd FlashEE

#'2'

cmp

beq

Check_Dump2

; continue if so

; else, respond to unknown command

qmţ

Check_What

```

```

Check_Dump1:

ldhx

#EE_StartAddr1

; point to start of 1st FlashEE

bra

Check_Dump3

; continue

Check_Dump2:

ldhx

#EE_StartAddr2

; point to start of 2nd FlashEE

Check_Dump3:

; initialize

lda

#8

psha

; line counter

txa

; perform

sub

#16

; 16-bit subtraction

psha

in order to adjust

pshh

FlashEE pointer

pula

;

backwards one dump

sbc

#0

;

print row

psha

and put pointer on the stack

Check_Dump4:

#msg_CRLF

; point to <CR><LF> message

ldhx

jsr

PrintString

; output it

pulh

; restore

pulx

; location pointer

#16

; add offset

aix

pshx

; save result

pshh

; back on stack

lda

#16

; initialize

; byte counter

psha

Check_Dump5:

#''

lda

; output

jsr

PutChar

; a space

, x

lda

; read FlashEE data

aix

#1

; move location pointer

; output it

jsr

PutHexByte

dbnz

1,sp,Check_Dump5

; loop back until all bytes done

pula

; deallocate stack usage

; loop back until all lines done

dbnz

3,sp,Check_Dump4

ais

; deallocate stack usage

#3

; loop back to top

jmp

main

;

Handle unknown commands.

Check_What:

ldhx

; point to unknown command message

#msg_what

jsr

PrintString

; output it

qmţ

main

; loop back to top

;* Messages

______

;*

$0D

ascii_CR:

equ

; ASCII carriage return

; ASCII line feed

ascii_LF:

equ

$0A

;

msq_hello:

db

ascii_CR,ascii_LF,'FlashEE>',0

msq_erased:

db

' FlashEE erased',0

' - what?',0

msq_what:

db

msq_CRLF:

db

ascii_CR,ascii_LF,0

```

```

;*

; *

This subroutine will output the null teminated string pointed to by H:X to the SCI.

; *

;*

Calling convention:

;*

; *

ldhx

#string

; point to start of string

; *

jsr

PrintString

; go output it

; *

;*

Returns:

nothing

;*

; *

Changes:

H:X

;*

PrintString1:

brclr

SCTE, scs1, PrintString1

; wait until SCI transmitter is empty

mov

x+,scdr

; output character to the SCI and advance pointer

PrintString:

tst

; test string character

PrintString1

bne

; loop back if not null

rts

; else, return

; *

; *

; *

This subroutine will output the character passed in ACC to the SCI.

; *

; *

C function prototype:

;*

; *

void PutChar (char data);

; *

; *

Calling convention:

; *

; *

lda

data

; get character

; *

PutChar

jsr

; go output it

;*

; *

Returns:

nothing

; *

; *

Changes:

nothing

; *

PutChar:

SCTE, scs1, PutChar

; wait until SCI transmitter is empty

brclr

scdr

; output character to the SCI

sta

; return

rts

; *

; *

;*

This subroutine will wait forever for a character to be received by the SCI and then

returns with that character in ACC. No error checking is performed. Note that this

; *

is the primary loop where the COP counter is cleared.

; *

; *

C function prototype:

; *

; *

char GetChar (void);

; *

; *

Calling convention:

; *

jsr

GetChar

; get a character from the SCI

```

36 MOTOROLA

AN2183

```

; *

; *

Returns:

; *

ACC= data

; *

GetChar:

sta

copctl

; clear the COP counter

SCRF, scs1, GetChar

; wait forever until SCI receiver is full

lda

scdr

; get data

rts

; return

; *

; *

; *

This subroutine converts the data in ACC to its two ASCII byte equivalent and outputs

; *

them via the SCI.

;*

; *

Calling convention:

; *

; *

lda

data

; *

jsr

PutHexByte

; *

; *

Returns:

nothing

; *

;*

ACC

Changes:

; *

PutHexByte:

; save ACC temporarily

psha

; move upper nibble down

nsa

FromHex

; convert it to ASCII

bsr

bsr

PutChar

; output it

; retrieve data

pula

; convert lower nibble to ASCII

bsr

FromHex

PutChar

bsr

; output it

; return

rts

; *

; *

; *

This subroutine retrieves two ASCII bytes via the SCI and converts (packs) them into one

; *

hex byte, which is returned in ACC.

; *

; *

Calling convention:

; *

; *

jsr

GetHexByte

; *

; *

Returns:

CCRZ= 1 if valid hex byte retrieved. Otherwise, CCRZ= 0.

; *

ACC= data

; *

; *

Changes:

ACC

; *

GetHexByte:

GetChar

; get msb character from the SCI

bsr

bsr

PutChar

; echo it back

bsr

IsHex

; check if valid ASCII hex character

bne

GetHexByte2

; exit if not

bsr

ToHex

; convert ASCII hex character to hex value

nsa

; swap lower nibble up

psha

; save temporarily

```

```

jsr

GetChar

; get 1sb character from the SCI

PutChar

; echo it back

bsr

bsr

IsHex

; check if valid ASCII hex character

bne

GetHexByte1

; exit if not

bsr

ToHex

; convert ASCII hex character to hex value

add

1,sp

; combine msb and lsb nibbles

bit

#0

; CCRZ= 1

GetHexByte1:

#1

; deallocate local variable

ais

GetHexByte2:

rts

; return

FromHex Subroutine -----

; *

; *

This subroutine converts the value passed in the lower nibble of ACC to it's ASCII

; *

equivalent.

; *

; *

Calling convention:

; *

; *

jsr

FromHex

; *

;*

Returns:

ACC= data.

;*

; *

Changes:

ACC

; *

FromHex:

; mask off upper nibble

#$0F

and

add

#'0'

; add ASCII offset for '0'

#'9'

; check if result is between '0' to '9'

cmp

bls

FromHex1

; skip if so

; else, adjust for value between 'A' to 'F'

add

#7

FromHex1:

; return

rts

; *

; *

; *

This subroutine converts the ASCII hex value passed in ACC to a binary hex value.

; *

; *

Calling convention:

; *

; *

lda

data

; *

jsr

ToHex

; *

; *

Returns:

ACC= data.

; *

;*

Changes:

ACC

; *

ToHex:

#'0'

; adjust first by subtracting '0'

sub

#9

; check if value was between '0' to '9'

cmp

bls

; exit if so

ToHex1

; else, adjust for value between 'A' to 'F'

sub

#7

ToHex1:

rts

; return

```

```

; *

; *

; *

This subroutine checks if the value passed in ACC is a valid ASCII hex character within

; *

within the ranges of '0' to '9' or 'A' to 'F' or 'a' to 'f'. Adjusts ACC if lowercase.

; *

;*

Calling convention:

; *

; *

lda

data

; *

jsr

IsHex

; *

; *

Returns:

CCRZ= 1 if data is a valid hex character. Otherwise, CCRZ= 0.

; *

;*

Changes:

ACC (if lowercsae)

; *

IsHex:

#'0'

; check value against '0'

cmp

; not hex if lower

blo

IsntHex

cmp

#'9'

; check value against '9'

; is hex if lower

bls

IsHex1

; check value against 'A'

cmp

#'A'

blo

IsntHex

; not hex if lower

#'F'

; check value against 'F'

cmp

IsHex1

; is hex if lower

bls

#$20

; adjust to uppercase

sub

#'A'

; check value against 'A'

cmp

blo

IsntHex

; not hex if lower

#'F'

; check value against 'F'

cmp

; isnt hex if higher

bhi

IsntHex

TsHex1:

bit

#0

; CCRZ= 1

IsntHex:

rts

; return

; *

;*

; *

This subroutine will program the CGM PLL to change the bus frequency in accordance with

; *

the data being pointed to by H:X.

; *

; *

Calling convention:

; *

; *

ldhx

#busfreq_table

; *

jsr

PLLset

; *

; *

Returns:

no data

; *

;*

Changes:

H:X

; *

PLLset:

bclr

BCS,pctl

; select external reference as base clock

bclr

PLLON, pctl

; turn off PLL

mov

x+,pctl

; program P & E

mov

x+,pmrs

; program L

mov

x+,pmsh

; program N msb

mov

x+,pmsl

; program N lsb

bset

AUTO, pbwc

; enable automatic bandwidth control

PLLON,pctl

bset

; turn on PLL

```

```

PLLwait:

.ifnot simulate

brclr LOCK,pbwc,PLLwait

; wait for PLL to lock

.endif

bset

BCS,pctl

; select VCO as base clock

rts

; return

;* 8.003584 MHz bus frequency parameters

;*

bus8003584:

db

$02

; P & E

$D0

db

; L

db

$03

; N msb

db

$D1

; N lsb

db

$01

; delay_msb

$F4

db

; delay_lsb

; SCI Baud Rate Register = 9600

db

%00110000

db

200

; LCD 100us delay parameter

;

;* 7.3728 MHz bus frequency parameters

;*

bus7372800:

$02

db

; P & E

$C0

db

; L

db

$03

; N msb

db

$84

; N lsb

db

$01

; delay_msb

db

$CC

; delay_lsb

db

%00010010

; SCI Baud Rate Register = 9600

db

184

; LCD 100us delay parameter

include "flashee.asm"

; include FlashEE routines

; *

Dummy:

rti

;*

; *

vec_timebase

; Timebase vector

org

dw

Dummy

vec_adc

; ADC vector

ora

dw

Dummy

org

vec_kbd

; Keyboard vector

dw

Dummy

vec_scitx

; SCI transmit vector

org

dw

Dummy

vec_scirx

; SCI receive vector

org

dw

Dummy

org

vec_scierr

; SCI error vector

dw

Dummy

; SPI transmit vector

org

vec_spitx

dw

Dummy

org

vec_spirx

; SPI receive vector

dw

Dummy

org

vec_tim2ov

; Timer 2 overflow vector

dw

Dummy

```

40 MOTOROLA

AN2183

| org | vec_tim2ch1 | ; | Timer 2 channel 1 vector |

|-----|-------------|---|--------------------------|

| dw  | Dummy       |   |                          |

| org | vec_tim2ch0 | ; | Timer 2 channel 0 vector |

| dw  | Dummy       |   |                          |

| org | vec_timlov  | ; | Timer 1 oveflow vector   |

| dw  | Dummy       |   |                          |

| org | vec_tim1ch1 | ; | Timer 1 channel 1 vector |

| dw  | Dummy       |   |                          |

| org | vec_tim1ch0 | ; | Timer 1 channel 0 vector |

| dw  | Dummy       |   |                          |

| org | vec_pll     | ; | PLL vector               |

| dw  | Dummy       |   |                          |

| org | vec_irq     | ; | IRQ vector               |

| dw  | Dummy       |   |                          |

| org | vec_swi     | ; | SWI vector               |

| dw  | Dummy       |   |                          |

| org | vec_reset   | ; | Reset vector             |

| dw  | Start       |   |                          |

|     |             |   |                          |

MOTOROLA 41

end

### gp32.equ

```

; *

MC68HC908GP32 Definitions

; *

Copyright (c) Derrick HJ Klotz, 2001

; *

; *

; *

Current Release Level:

File name:

gp32.equ

; *

Last Edit Date:

Classification:

; *

; *

Include Files:

; *

; *

Assembler:

P&E's CASM08

Version:

3.06

; *

;*

Target Device:

MC68HC908GP32

;*

;*

Documentation:

MC68HC908GP32/H Rev 3 Microcontroller Technical Data

;*

; *

;*

Author:

DHJ Klotz

Location: TOR

;*

First Release:

22-Feb-00

; *

; *

Update History:

; *

; *

Rev

Date

Author Description of Change

; *

_____

; *

ES 1.0 22-Feb-00 DHJK

Initial release.

; *

; *

; *

Motorola reserves the right to make changes without further notice to any product

; *

herein to improve reliability, function, or design. Motorola does not assume any

; *

liability arising out of the application or use of any product, circuit, or software

; *

described herein; neither does it convey any license under its patent rights nor the

; *

rights of others. Motorola products are not designed, intended, or authorized for

; *

use as components in systems intended for surgical implant into the body, or other

; *

applications intended to support life, or for any other application in which the

; *

failure of the Motorola product could create a situation where personal injury or

; *

death may occur. Should Buyer purchase or use Motorola products for any such

; *

intended or unauthorized application, Buyer shall indemnify and hold Motorola and

; *

its officers, employees, subsidiaries, affiliates, and distributors harmless against

all claims, costs, damages, and expenses, and reasonable attorney fees arising out

;*

;*

of, directly or indirectly, any claim of personal injury or death associated with

such unintended or unauthorized use, even if such claim alleges that Motorola was

; *

; *

negligent regarding the design or manufacture of the part.

; *

; *

Motorola and the Motorola logo are registered trademarks of Motorola Ltd.

```

```

;* Memory Map and Interrupt Vectors

; *

ram_start:

equ

$0040

; start of RAM

ram_last:

$023F

; last RAM location

eau

rom_start:

eau

$8000

; start of ROM

rom_last:

$FDFF

; last ROM location

equ

$FFDC

; Timebase vector

vec_timebase: equ

$FFDE

; ADC vector

vec_adc: equ

vec_kbd:

equ

$FFE0

; Keyboard vector

equ

vec_scitx:

$FFE2

; SCI transmit vector

; SCI receive vector

vec_scirx:

$FFE4

equ

; SCI error vector

vec_scierr:

$FFE6

equ

vec_spitx:

equ

$FFE8

; SPI transmit vector

vec_spirx:

equ

$FFEA

; SPI receive vector

vec_tim2ov:

$FFEC

; Timer 2 overflow vector

equ

vec_tim2ch1: equ

$FFEE

; Timer 2 channel 1 vector

; Timer 2 channel 0 vector

vec_tim2ch0: equ

$FFF0

; Timer 1 oveflow vector

vec_timlov:

equ

$FFF2

; Timer 1 channel 1 vector

vec_tim1ch1: equ

$FFF4

; Timer 1 channel 0 vector

vec_tim1ch0: equ

$FFF6

; PLL vector

vec_pll: equ

$FFF8

; IRQ vector

vec_irq:

equ

$FFFA

$FFFC

; SWI vector

vec_swi:

equ

$FFFE

vec_reset:

equ

; Reset vector

;* Input/Output (I/O) Ports

*****************

; *

$00

porta:

equ

; Port A Data Register

$01

; Port B Data Register

portb:

equ

$02

; Port C Data Register

portc:

equ

$03

; Port D Data Register

portd:

equ

$04

ddra:

; Port A Data Direction Register

equ

$05

ddrb:

; Port B Data Direction Register

equ

$06

; Port C Data Direction Register

ddrc:

equ

$07

; Port D Data Direction Register

ddrd:

equ

$08

; Port E Data Register

porte:

equ

$0C

; Port E Data Direction Register

ddre:

equ

$0D

; Port A Input Pullup Enable Register

ptapue:

equ

$0E

; Port C Input Pullup Enable Register

ptcpue:

eau

ptdpue:

$0F

; Port D Input Pullup Enable Register

eau

;* Serial Peripheral Interface Module (SPI)

************

; *

$10

; SPI Control Register

spcr:

eau

SPRIE:

equ

7

; SPI receiver interrupt enable bit

SPMSTR:

egu

5

; SPI master bit

CPOL:

eau

4

; clock polarity bit

CPHA:

equ

3

; clock phase bit

; SPI wired-or mode bit

SPWOM:

2

eau

; SPI enable

SPE:

1

eau

SPTIE:

equ

Ω

; SPI transmit interrupt enable

```

```

$11

; SPI Status and Control Register

spscr:

equ

; SPI receiver full bit

SPRF:

eau

; error interrupt enable bit

ERRIE:

equ

OVRF:

equ

5

; overflow bit

MODF:

; mode fault bit

eau

SPTE:

eau

; SPI transmitter empty bit

2

; mode fault enable bit

MODFEN:

equ

SPR1:

1

; SPI baud rate

equ

SPR0:

0

; select bits

equ

spdr:

$12

; SPI Data Register

;* Serial Communications Interface (SCI)

; *

scc1:

equ

$13

; SCI Control Register 1

LOOPS:

7

; loop mode select bit

equ

ENSCI:

6

; enable SCI bit

eau

5

; transmit inversion bit

TXINV:

equ

4

м:

; mode bit

WAKE:

3

; wakeup condition bit

2

TITY:

equ

; idle line type bit

1

; parity enable bit

PEN:

equ

0

PTY:

equ

; parity bit

scc2:

equ

$14

; SCI Control Register 2

7

; SCI transmit interrupt enable bit

SCTIE:

equ

TCIE:

6

; transmission complete interrupt enable bit

equ

5

SCRIE:

; SCI receive interrupt enable bit

equ

TLIE:

4

; idle line interrupt enable bit

equ

; transmitter enable bit

TE:

equ

3

RE:

2

; receiver enable bit

equ

RWII:

1

; receiver wakeup bit

equ

0

SBK:

; send break bit

equ

; SCI Control Register 3

scc3:

$15

equ

; received bit 8

R8:

7

equ

T8:

; transmitted bit 8

6

equ

DMARE:

5

; DMA receive enable bit

equ

DMATE:

4

; DMA transfer enable bit

equ

; receiver overrun interrupt enable bit

ORIE:

3

eau

NEIE:

2

; receiver noise error interrupt enable bit

eau

FEIE:

1

; receiver framing error interrupt enable bit

eau

PEIE:

0

; receiver parity error interrupt enable bit

eau

;

scs1:

ean

$16

; SCI Status Register 1

; SCI transmitter empty bit

SCTE:

7

eau

TC:

6

; transmission complete bit

eau

SCRF:

5

; SCI receiver full bit

eau

IDLE:

4

; receiver idle bit

eau

OR:

eau

3

; receiver overrun bit

NF:

2

; receiver noise flag bit

eau

FE:

1

; receiver framing error bit

eau

PE:

equ

; receiver parity error bit

```

```

$17

; SCI Status Register 2

scs2:

equ

equ

1

; break flag bit

RPF:

0

; reception in progress flag bit

equ

scdr:

equ

$18

; SCI Data Register

scbr:

equ

$19

; SCI Baud Rate Register

;* Keyboard Interrupt Module (KBI)

*****************

;*

intkbscr:

$1A

; Keyboard Status and Control Register

3

; keyboard flag bit

ACKK:

2

; keyboard acknowledge bit

equ

IMASKK:

1

; keyboard interrupt mask bit

equ

MODEK:

equ

0

; keyboard triggering sensitivity bit

intkbier:

equ $1B

; Keyboard Interrupt Enable Register

KBIE7:

7

equ

6

KBIE6:

equ

KBIE5:

5

equ

KBIE4:

4

equ

3

KBIE3:

equ

2

KBIE2:

equ

KBTE1:

equ

1

KBTEO:

0

equ

;* Timebase Module (TBM)

********************

; *

tbcr:

equ $1C

; Timebase Control Register

TBIF:

equ

7

; timebase interrupt flag

6

TBR2:

; \

equ

5

TBR1:

; timebase rate selection

equ

4

TBR0:

; /

equ

3

TACK:

; timebase acknowledge

equ

TBIE:

2

; timebase interrupt enable

equ

TBON:

1

; timebase enabled

equ

;* External Interrupt (IRQ)

*******************

; *

equ $1D

; IRQ Status and Control Register

intscr:

3

; IRQ flag bit

IRQF:

equ

2

ACK:

; IRQ interrupt request acknowledge bit

equ

1

IMASK:

equ

; IRQ interrupt mask bit

MODE:

equ

0

; IRQ edge/level select bit

;* Configuration Registers (CONFIG)

*****************

; *

config2: equ $1E

config1: equ $1F

; Configuration Register 2

; Configuration Register 1

```

```

;* Timer Interface module (TIM)

****************

; *

t1sc:

$20

; Timer 1 Status and Control Register

t2sc:

equ

$2B

; Timer 2 Status and Control Register

equ

7

; TIM overflow flag bit

TOIE:

6

; TIM overflow interrupt enable bit

TSTOP:

5

; TIM stop bit

equ

; TIM reset bit

TRST:

equ

2

PS2:

equ

; \

PS1:

equ

1

; prescaler select bits

PS0:

0

equ

t1sc0:

$25

; Timer 1 Channel 0 Status and Control Register

t1sc1:

$28

; Timer 1 Channel 1 Status and Control Register

$30

t2sc0:

equ

; Timer 2 Channel 0 Status and Control Register

t2sc1:

$33

; Timer 2 Channel 1 Status and Control Register

CHxF:

7

; channel x flag bit

6

CHxIE:

equ

; channel x interrupt enable

5

MSxB:

eau

; channel x mode select bit B